Page 24 - 第4部応用事例編ver60_Neat

P. 24

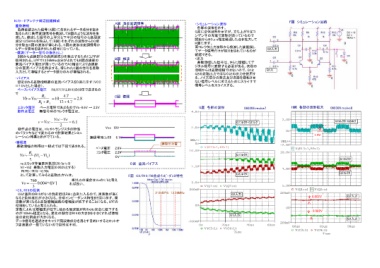

ICカードアンテナ周辺回路構成 A図 負荷変調信号 ・シミュレーション波形 F図 シミュレーション回路

B図 検波 各部の波形を示す。

差動増幅 C図 復調 G図に全体波形を示すが、立ち上がりはコ Q2入力

負荷変調された信号(A図)に含まれるデータ成分を抜き ンデンサの充電で波形が踊っているので Q1入

取るために負荷変調信号を検波してB図のような波形を生 開始から80μs程度経過した点を拡大して

成した。検波した信号の上半分と下半分の信号から高周波 H図に示す。

成分13.56MHzを除去して(B図)それぞれの波形からDC成 両コレクタ出力波形から検波した後復調し

分を除去C図の波形が得られる。C図の波形は変調信号か てデータ信号だけが取り出されているのが

らデータ信号を抜き出した信号になっている。 確認できる。

・復調(データー信号の抜き出し) ・出力

B図から点線部分の高周波成分を除去するためにLPFが 差動増幅した信号は、さらに増幅してデ

使用される。LPFで13.56MHz成分がとれてもB図点線部の ジタル信号に変換する必要がある。次段の

直流バイアス電圧が残っているのでAC結合により点線部 増幅からは差動増幅ではないので、Q1と

分の直流バイアスを除去する。得られたC図の信号を差動 Q2の差動出力ではなくQ2の出力を使用す

入力として増幅するとデータ部分のみが増幅される。 る。ノイズ成分の除去及び次段を飽和させ

ない信号レベルに抑えるためにスライサで

・バイアス 信号レベルをスライスする。

想定される差動増幅器の直流バイアスをD図に示す(VCC

=10Vとした場合)。 G図 各部の波形 060306 recive7 H図 各部の波形拡大 060306 recive8

ベースバイアス電圧 R8,R7(R12,R11)の分圧で決まるの 4.0V

で

Vb = Vcc R7 = 10 4.7 = 2.8

R8 + R 7 12 + 4.7

エミッタ電圧 ベース電圧で決まるのでVb-0.6V → 2.2V

動作点電圧 無信号時のコレクタ電圧は、

v = Vcc − Vcc −Ve = 6.1 Q1コレクタ-Q2コレク 2.0V Q1コレクタ-Q2コレク

2 タ タ

Vcc 10V 2.0V

動作点の電圧は、Hfeやトランジスタの特性 無信号時コレクタ 6.1V Q1コレクタ

0V Q2コレクタ

のバラツキなどで変わるので計算結果とシミュ 1.4V

レーション結果と差がでている。

・増幅度 ベース電圧 2.8V 差動出力電 SEL>> V(R13:1,R9:1) SEL>> V(R13:1,R9:1)

差動増幅の利得は一般式では下記で表される。 エミッタ電圧 2.2V 圧 0V -2.5V

RL 0V 10.0V 10.0V

re

Vo≒ (Vi1 −Vi2 ) Q1コレクタ

re:エミッタ等価直列抵抗(26/Ie≒3) D図 直流バイアス

Vi1-Vi2 差動入力電圧(0.002Vとする) 7.5V 7.5V

Rl:R9//R19→0.76k Q2コレクタ

として計算してみると差動出力Voは、 E図 C8/R19/R9合成インピーダンス特性

Vo = 760 0.004≒1[V ] 単出力の場合はVoの1/2と考え 5.0V V(Q1:c) V(Q2:c) 5.0V

3 れば良い。 Q2入力 200mV

200mV

・C8、R19の役割 212kBPS 13.56MHz V(Q1:c) V(Q2:c)

0.002V

C8と直列のR19がQ1の負荷抵抗R9に並列に入るので、周波数が高く Q2入力

なると負荷抵抗が小さくなる。合成インピーダンス特性をE図に示す。周 Q1入力

90us

波数が高くなると差動増幅回路の増幅度が低下することになる。LPFの

役割をしていると考えられる。 0V

定数によれば増幅度が低下し始める周波数が約1kHz完全に低下する 0V

0.002V

のが100kHz程度となる。変化の割合はR19の大きさを小さくすれば増幅

Q1入力

度の変化割合が大きくなる。

データ信号を通過させキャリア周波数成分を落とす目的にするとカットオ -200mV -200mV

0s

フ周波数が一致ていないので目的は不明。 V(C3:1) 20us 40us 60us 80us 85us

V(C4:1) V(C4:1)

Time V(C3:1)

Time